728x90

반응형

- Uniprocessor performance improvement

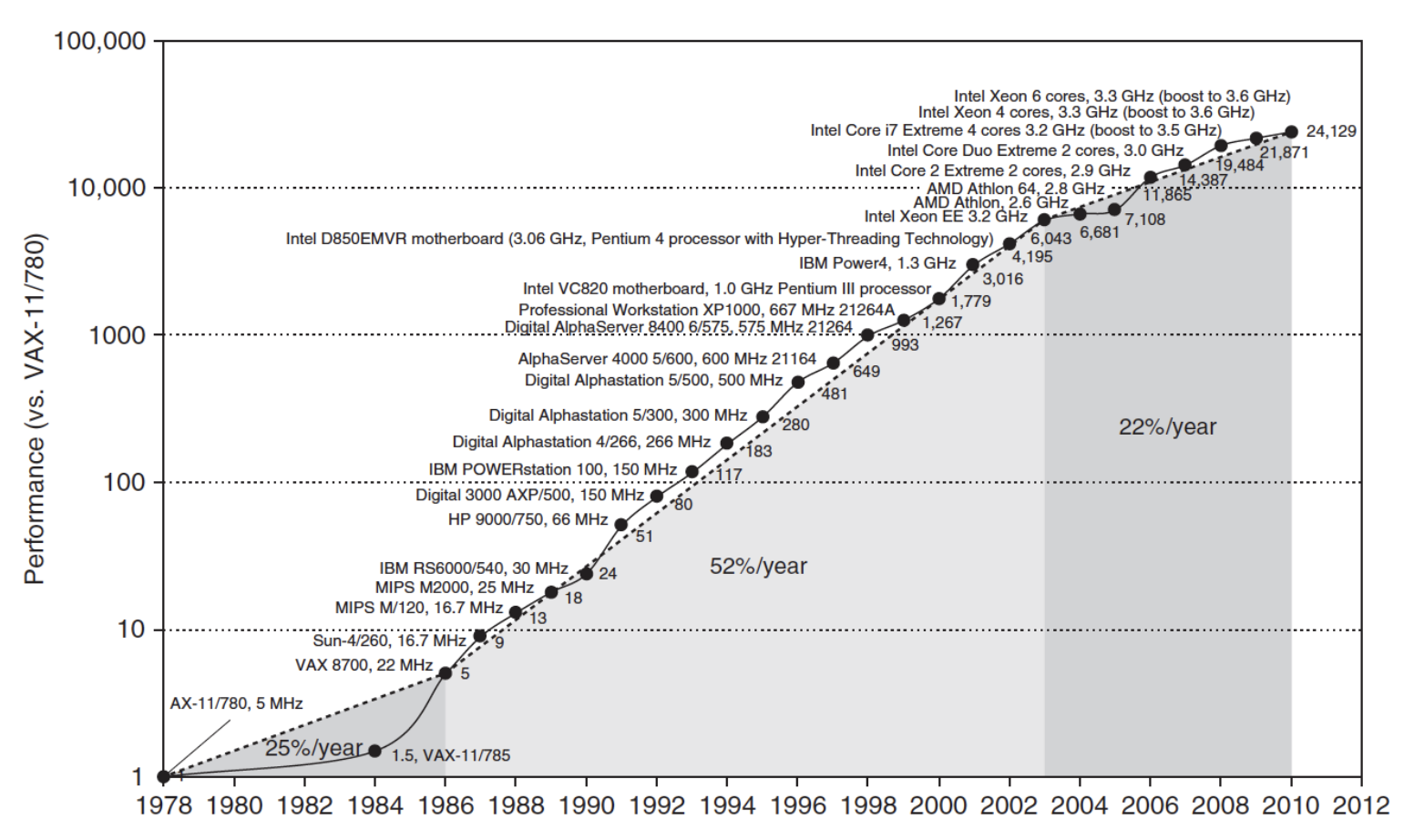

1986년도 부터 2003년 정도까지는 해마다 단일 프로세서의 성능이 급격하게 증가했지만, 그 이후로 다시 정체되는 모습을 보이고 있습니다. Clock speed를 높임에 따라서 늘어나는 성능보다는 배터리 전력소모 등의 단점이 더 커져갔기 때문입니다. 기존의 컴퓨터 아키텍쳐를 통해서 Parallel하게 Instruction을 수행할 수 있도록 design하는 방법이 한계에 달했다고 볼 수 있습니다.

아무리 프로세서를 빠르게 만들어도 메모리 접근을 자주하게 되면 여전히 메모리 속도는 상대적으로 느리기 때문에 속도가 감소하게 됩니다. 즉 빠른 프로세서가 큰 영향을 못 미치는 상황인 것입니다.

- Processor

- Logic capacity: 칩 안에 넣을 수 잇는 트랜지스터의 개수. Improved about 30% per year

- Clock rate: CPU가 초당 실행하는 사이클의 수. Improved about 20% per year

- Memory

- DRAM capacity: Improved about 60% per year (4x every 3 years)

- Memory speed: Improved about 10% per year (메모리의 속도 자체는 크게 증가하지 않음) -> Processor와의 속도 차이 점점 커짐

- Cost per bit: Improved about 25% per year

- Disk

- Capacity: Improved about 60% per year

- Moore's law

- 마이크로칩 기술의 발전 속도에 관한 일종의 법칙으로 마이크로칩에 저장할 수 있는 데이터 분량이 18-24개월 마다 두 배씩 증가한다는 법칙

- 컴퓨터 성능이 거의 5년마다 10배, 10년마다 100배씩 개선된다는 것을 의미

- The number of transistors per integrated circuit would double every 18 months

- Development of computer architecture

- 병렬 구조의 활용(Exploiting parallelism)

- Single processor를 병렬적으로 활용해서 성능 개선

- Pipelining

- Superscalar: 하나의 칩 안에 연산장치가 여러개 들어가 있는 구조

- VLIW(Very Long Instruction Word): 여러 opcode 필드가 있는 긴 명령어 하나에 독립적인 연산 여러개를 정의하고 한꺼번에 내보내는 명령어 구조 집합

- Single processor를 병렬적으로 활용해서 성능 개선

- Multiprocessor: 프로세서를 여러 개 사용. 보통 프로세서(core) 하나하나가 Superscalar processor

- Media Instruction(SIMD): 하나의 Instruction으로 여러 개의 데이터를 처리하는 방식

- Cache Memory: 빠른 속도의 프로세서와 느린 속도의 메모리 사이에 작고 빠른 캐시 메모리를 두어 메모리 접근 최소화

- Eight Great Ideas

- Design for Moore's Law

- Use abstraction to simplify design

- 소프트웨어 엔지니어는 하드웨어의 내부를 몰라도 하드웨어의 abstracted된 인터페이스만 알면 전체적인 하드웨어를 사용할 수 있다.

- Make the common case fast

- 자주 발생하는 case를 빠르게 설계하는 것을 목표로 해라.

- Performance via parallelism

- Performance via pipelining

- 여러 instruction의 수행을 중첩(overlap)시킨다.

- Performance via prediction

- Hierarchy of memories

- Processor에 가까울수록 빠르지만 작은 사이즈의 메모리를 사용하게된다. (멀먼 느리지만, 사이즈는 큼)

- 계층구조를 이용해서 Processor에게는 마치 큰 용량의 메모리가 있는 것처럼 보이게 한다. (자주 쓰는 것을 가까이 둔다)

- Dependability via redundancy

- 여러 개의 장치들을 중복해서 가지고 있으면 그 중에 하나가 고장나더라도 전체 시스템은 계속 가동 가능하다.

- Computer system

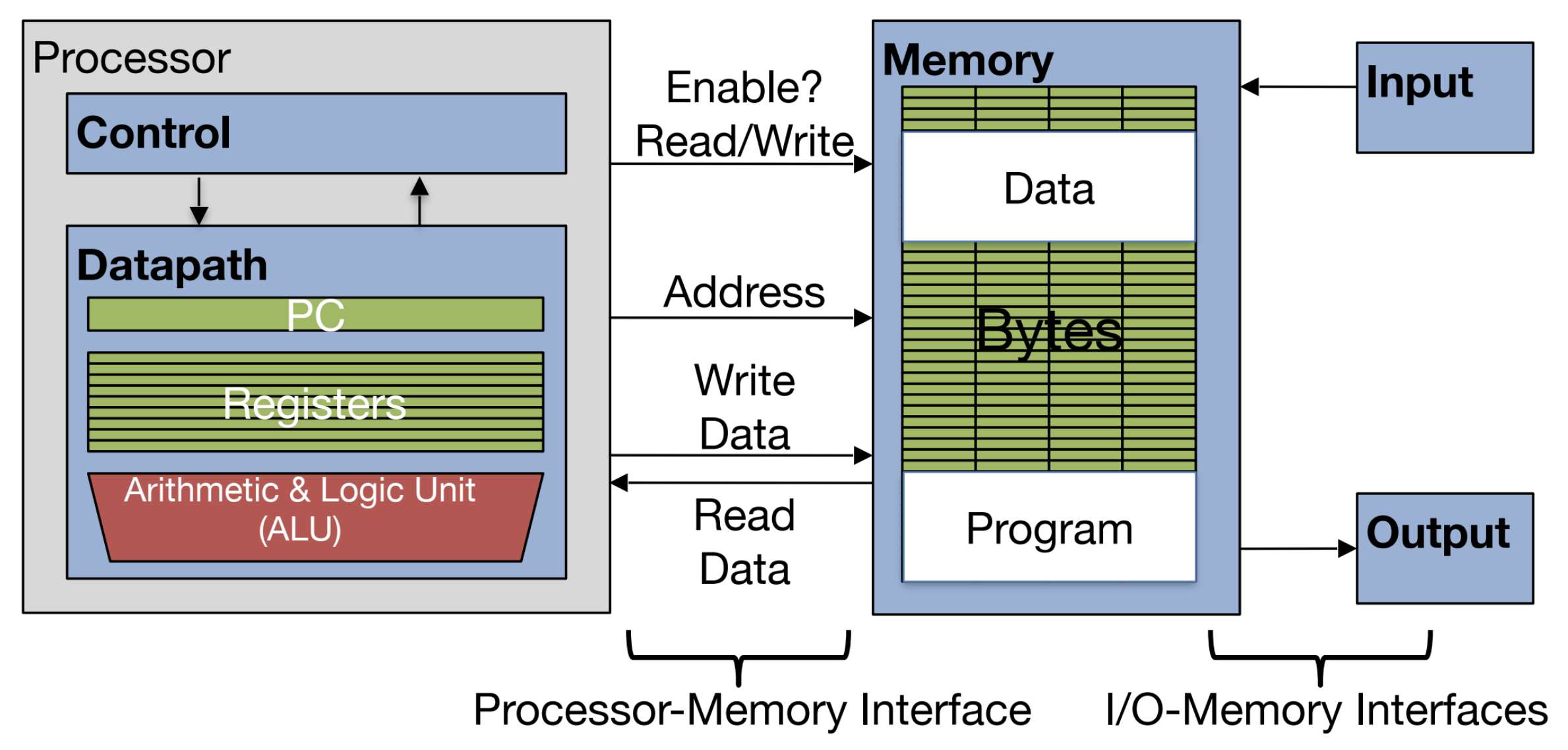

- Datapath: 산술 연산을 실행한다.

- Control: datapath, memory, I/O devices가 무엇을 할지 알려준다.

- Sequential execution

각 명령을 작성된 순서에 따라 순차적으로 실행하고, program counter의 값을 하나씩 증가시키면서 다음 실행 순서를 결정하는 방식

- Fetch: 메모리에 있는 Instruction을 프로세서가 가지고 온다.

- Decode: 가져온 Instruction을 읽어서 해석한다.

- Execution: 해석한 내용을 따라서 실행한다.

- 다시 Fetch로 돌아가서 다음 Instruction을 읽어오면서 프로그램이 끝날 때까지 반복

* program counter: 메모리 Instruction의 특정한 위치를 가리킨다.

728x90

반응형

'Computer Science > Computer Architecture' 카테고리의 다른 글

| [Computer Architecture] Performance (1) | 2024.01.23 |

|---|---|

| [Computer Architecture] ISA(Instruction Set Architecture) (0) | 2024.01.10 |

| [Computer Architecture] Computer Abstractions and Technology (1) | 2024.01.08 |

| [Computer Architecture] Performance (0) | 2023.12.30 |

| [Computer Architecture] Computer abstraction & Technology (0) | 2023.12.30 |