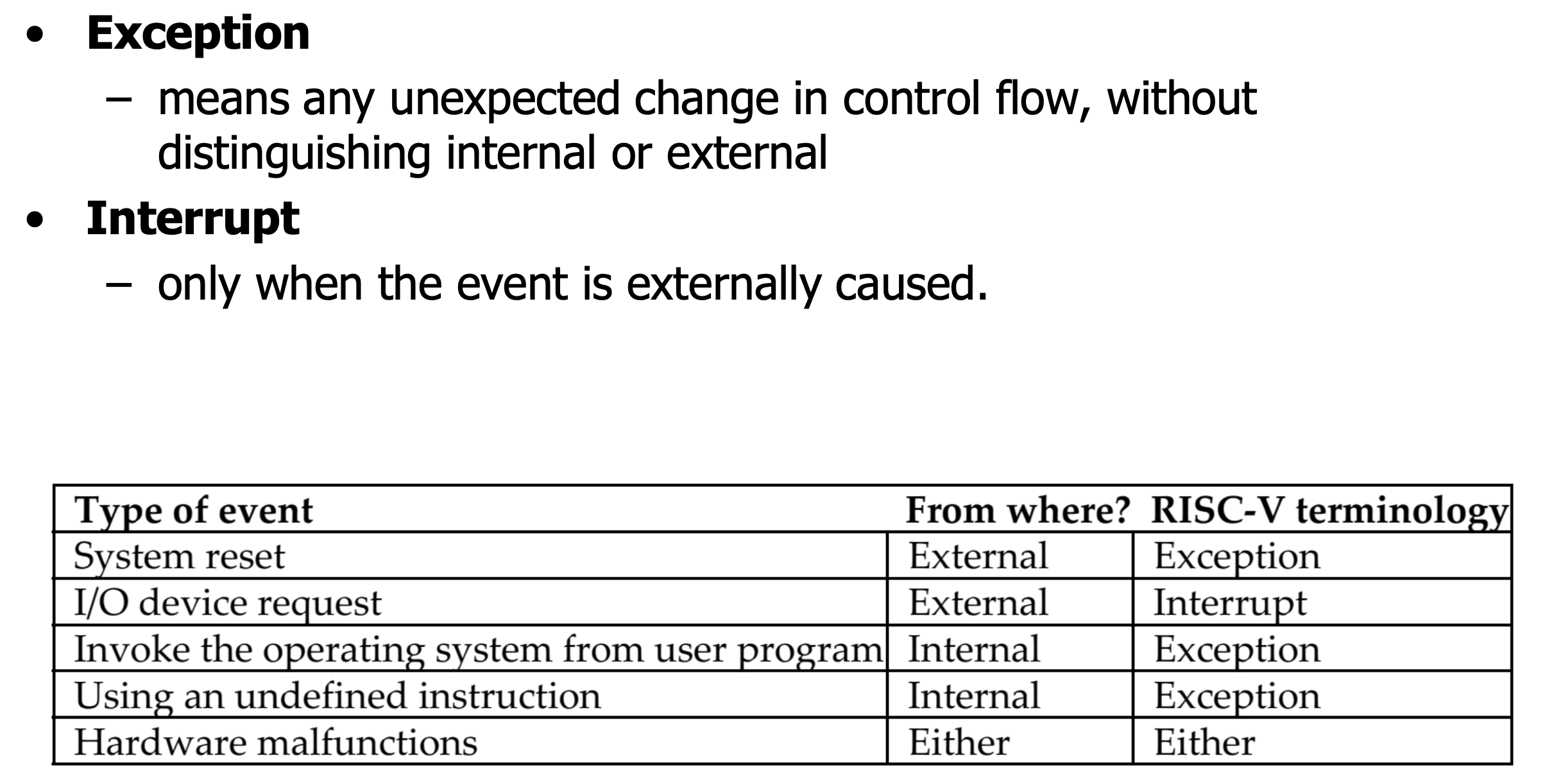

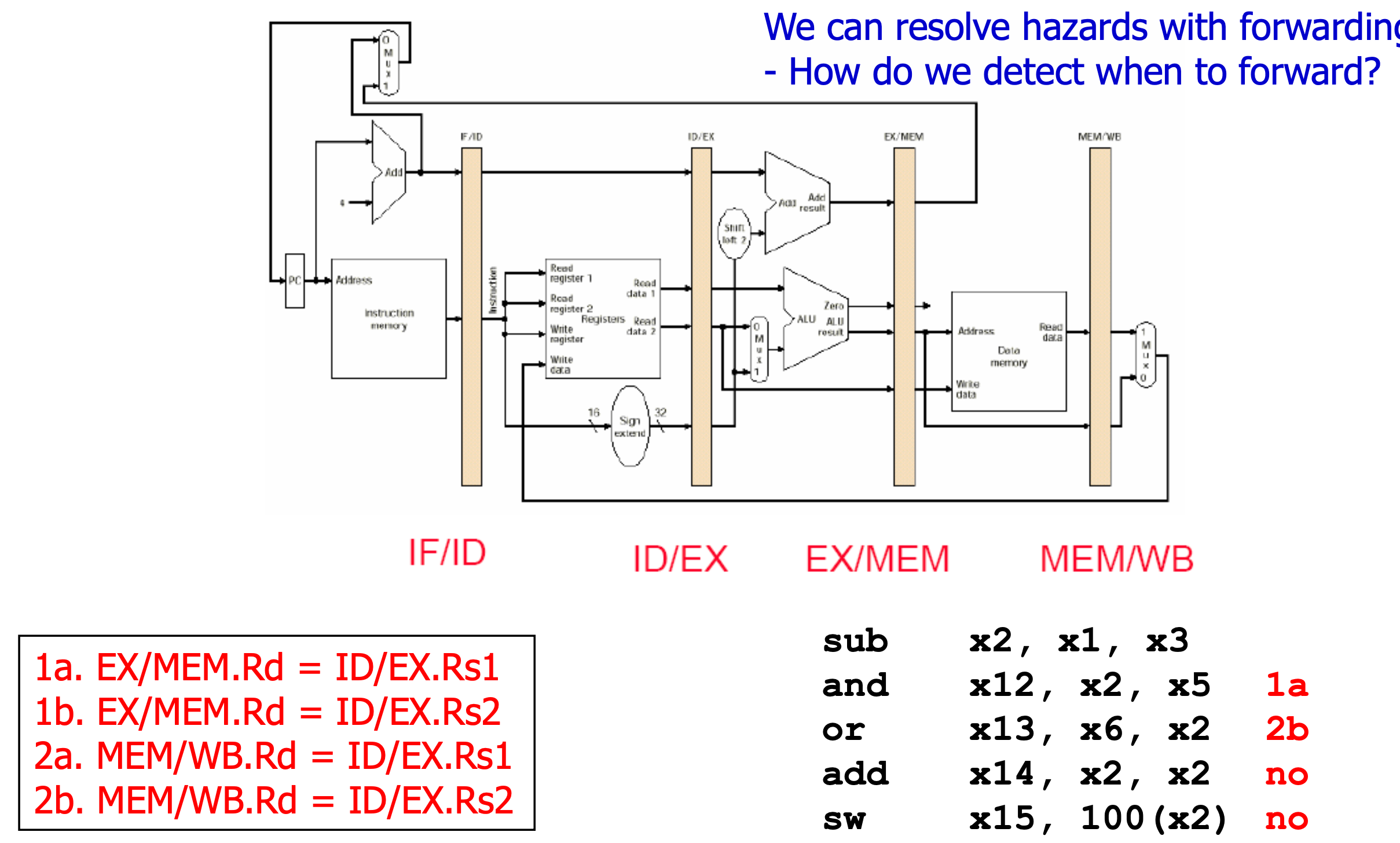

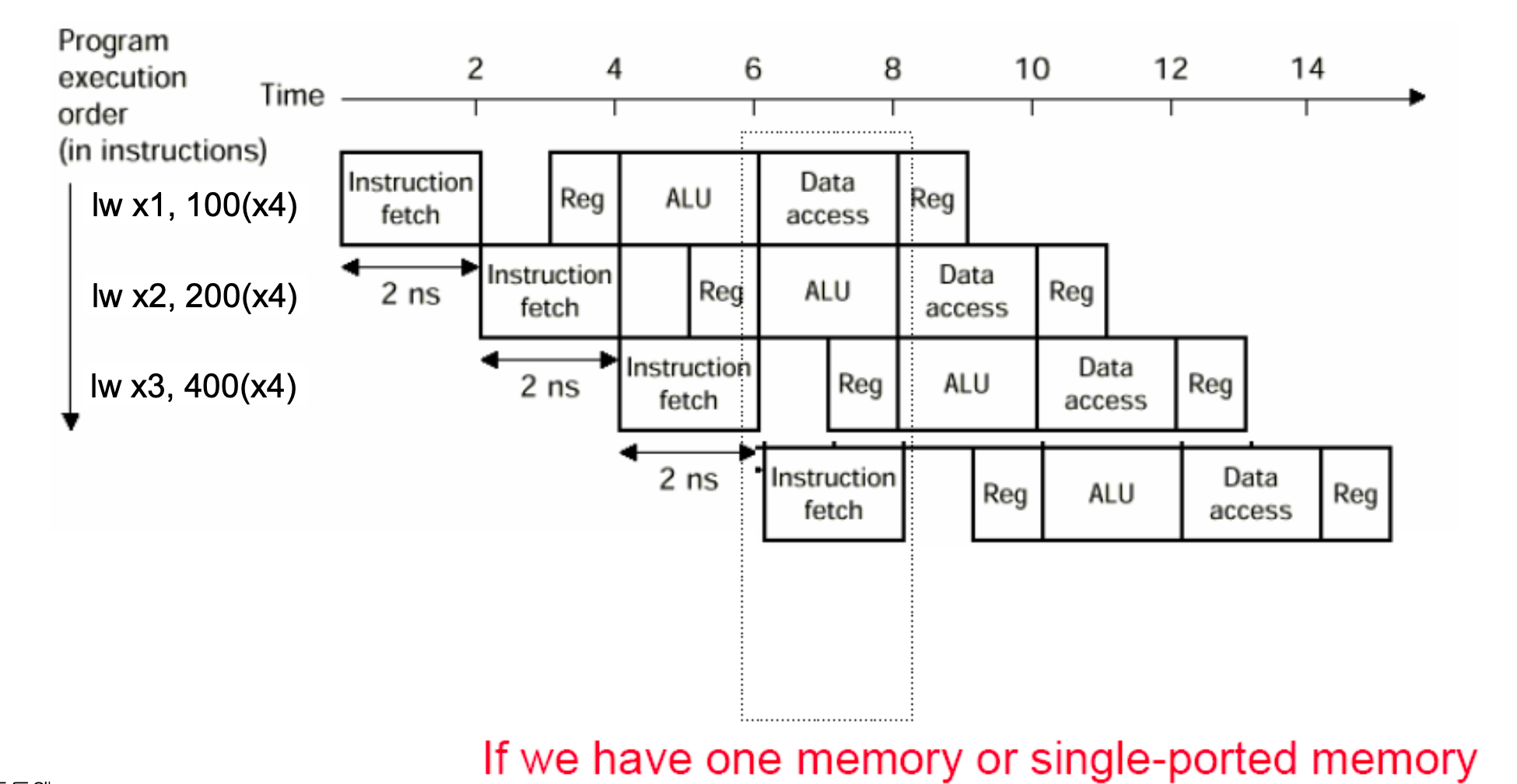

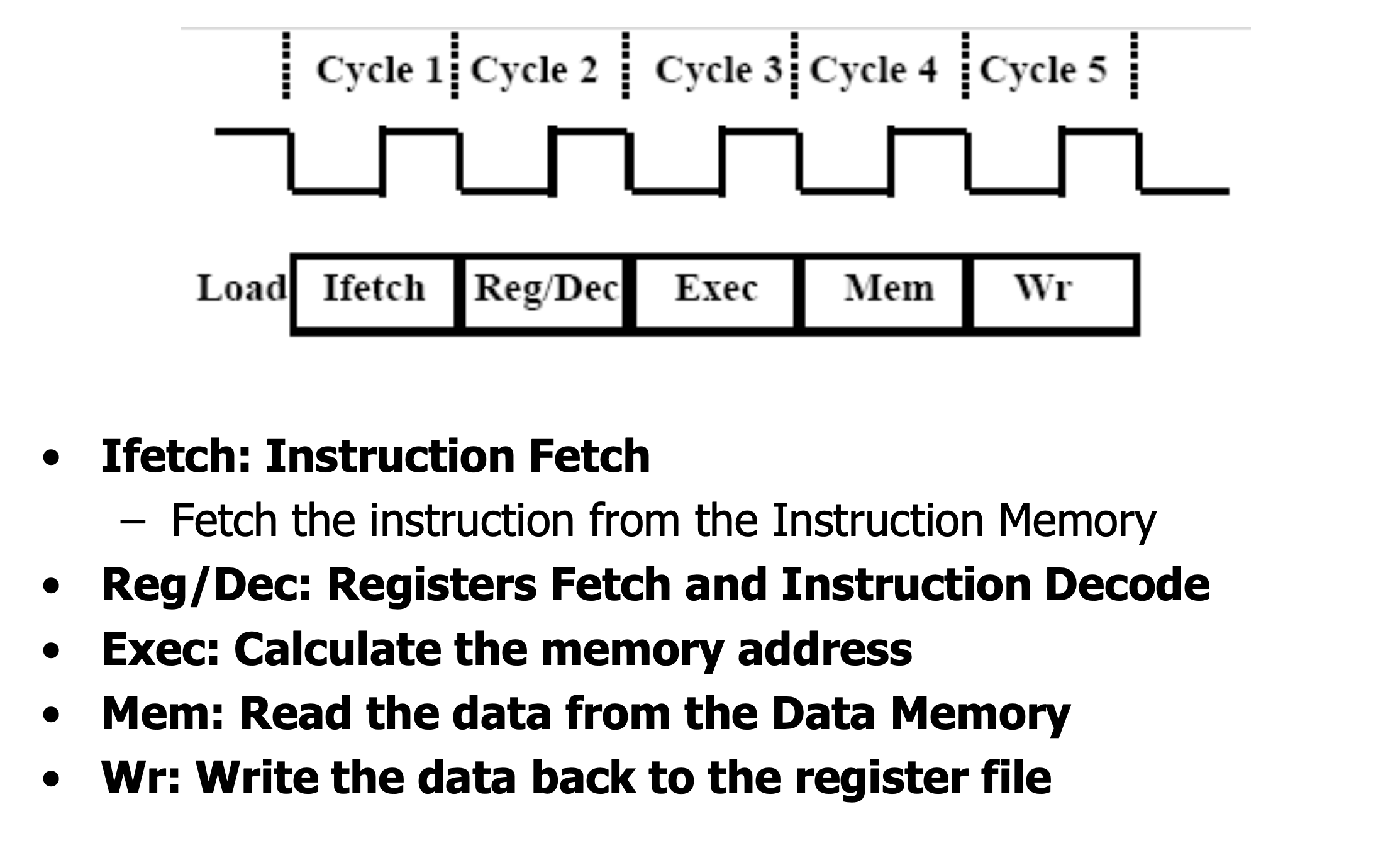

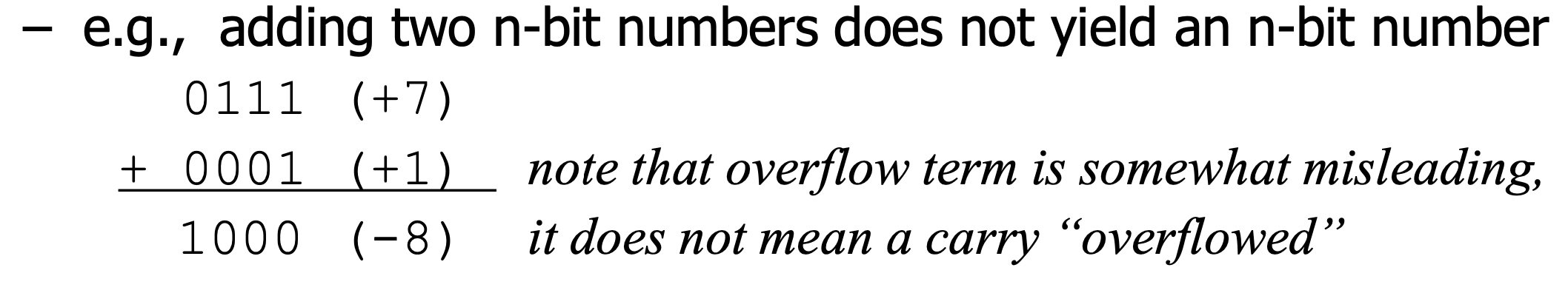

Exception unscheduled event that disrupt program excution(프로그램의 실행을 멈춤) User program의 Instruction을 수행하다가 문제사항이 생기게 되면 그 문제를 해결할 수 있는 OS 안에 위치하는 Exception handler을 이용하기 위해 OS에게 해결해달라고 소프트웨어에게 알리는 것입니다. 즉, 하드웨어가 소프트웨어에게 알리고 소프트웨어가 OS에게 handling 해달라고 부탁하게 됩니다. Exception 처리가 끝난 뒤에는 다시 원래 지점으로 돌아와서 진행하게 됩니다. (returns control to user) Exception 종류 Interrupts CPU 바깥의 event로 인해서 일어나는 Exception (caused b..