728x90

728x90

Exception

- unscheduled event that disrupt program excution(프로그램의 실행을 멈춤)

- User program의 Instruction을 수행하다가 문제사항이 생기게 되면 그 문제를 해결할 수 있는 OS 안에 위치하는 Exception handler을 이용하기 위해 OS에게 해결해달라고 소프트웨어에게 알리는 것입니다.

- 즉, 하드웨어가 소프트웨어에게 알리고 소프트웨어가 OS에게 handling 해달라고 부탁하게 됩니다.

- Exception 처리가 끝난 뒤에는 다시 원래 지점으로 돌아와서 진행하게 됩니다. (returns control to user)

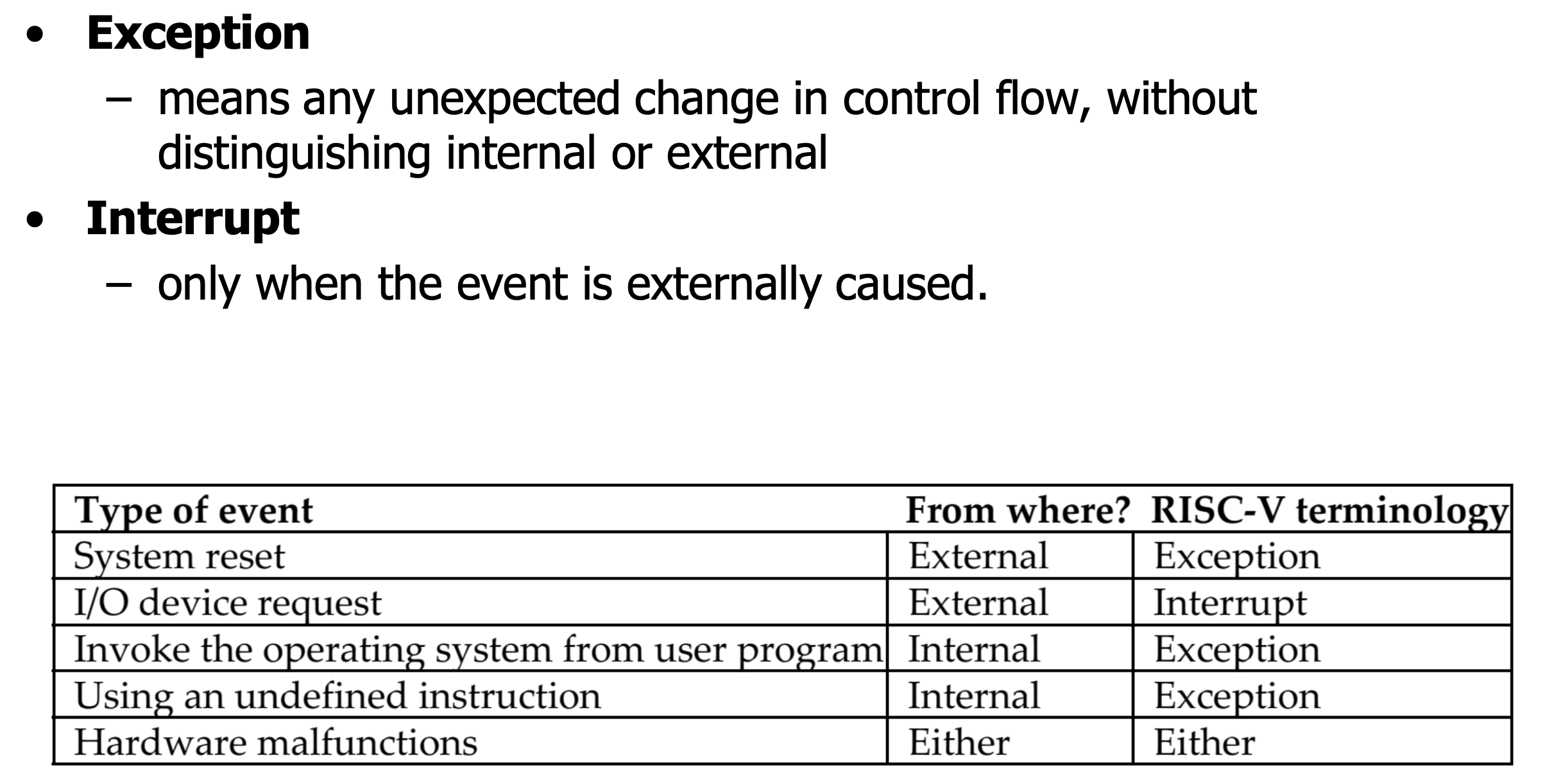

- Exception 종류

- Interrupts

- CPU 바깥의 event로 인해서 일어나는 Exception (caused by external events)

- 즉, 프로그램을 수행하다가 발생하는 것이 아니라 그것과 무관하게 외부에서 갑작스럽게 발생하는 event로 일어나는 exception

- Instruction들 사이에서만 처리되면 됩니다. (바로 처리할 필요없음)

- 어떤 Instruction을 수행하고 있을 때, Interrupt가 발생하면 Instruction을 다 끝내고 Interrupt에 대해 핸들링해도 문제가 없습니다.

- simply suspend and resume user program

- Traps

- 수행 중이던 프로그램에 의해서 일어나는 Exception (caused by internal event)

- 발생하는 즉시 문제를 해결하기 위해 넘어가야 합니다.

- Access fault: 메모리 접근에 문제가 발생. 특히 접근하려고 하는 메모리 주소가 접근 불가능한 경우 발생

- Breakpoint: ebreak instruction을 실행했을 때, debuger program으로 jump(break point를 쓰기위한 명령)

- Envrionment call: ecall instruction을 실행했을 때 발생(system call을 유발했을 때)

- illegal instruction: invalid opcode를 decoding하려고 했을 때 발생(undefined instruction)

- Misaligned address: 접근하는 메모리 주소 값이 안맞을 때, align이 안되어있을 때 (when the effective address isn't divisible by the access size)

- Interrupts

RISC-V Exception Handling

- 전용 레지스터 sepc(mepc)에 PC를 저장합니다.

- 중단된 프로그램의 실행을 완료하기 위해 필요한 ra의 값이 덮어쓰여질 수 없기 때문입니다.

- procedure call을 할 때, Return address를 ra register에 저장을 했었는데, exception의 경우에는 원래 프로그램이 의도한 control flow가 아니기에 procedure call과 비슷해보이지만 ra register를 사용할 수 없습니다.

- 예외의 이유를 scause(mcause) 레지스터에 기록합니다.

- 현재 ra register에는 돌아올 main function의 주솟값이 저장되어 있습니다. exception을 처리할 때 ra register overwrite를 하면 돌아올 주솟값을 잊어버리게 되므로 건들면 안됩니다. (exception은 별도의 register에서 처리)

- PC에 특별한 값을 로드합니다. 이는 예외 처리기의 주소(PC ← 0x1C090000)입니다.

- 벡터 인터럽트와 비교할 때, 예외 처리기의 주소는 예외의 원인에 따라 결정됩니다.

- Undef: PC ← b00 0100 000

- 시스템 에러: PC ← b01 1000 0000

- 명령어 sret(mret)은 sepc(mepc)에서 PC를 복원합니다.

728x90

300x250

'Computer Science > Computer Architecture' 카테고리의 다른 글

| [Computer Architecture] Hazard Detection (0) | 2024.03.03 |

|---|---|

| [Computer Architecture] Pipeline Hazards (0) | 2024.03.03 |

| [Computer Architecture] Enhancing Performance with Pipelining (0) | 2024.03.03 |

| [Computer Architecture] Datapath (0) | 2024.02.29 |

| [Computer Architecture] Clocking Methodology (1) | 2024.02.29 |